반도체 업계의 1nm 시대가 성큼 다가오고 있다. TSMC는 대만 타이난(Tainan) 사룬(Shanhua) 지역에 1nm 반도체 공장을 건설할 계획이다. 특히, 이번 1nm 공정에서는 기존 핀펫(FinFET)에서 게이트 올 어라운드(GAA) 기술을 적용해 성능과 전력 효율을 더욱 향상할 예정이다.

✅ 1nm 공장, 어디에서 건설되나?

대만 연합보(聯合報) 보도에 따르면, TSMC는 대만 남부 타이난 사룬 지역에 새로운 **‘25 팹(fab)’**을 건설할 예정이다.

📍 공장 예상 위치:

1. 타이난 사룬 지역(Southern Taiwan Science Park, STSP 내)

2. 6개 공장 규모의 초대형 팹(Fab 25) 건설 예정

TSMC는 초미세 공정을 위해 대규모 생산 인프라를 구축하고 있으며, 이 공장은 향후 1nm 및 그 이하 공정까지 담당할 가능성이 높다.

🔎 25 팹 공장의 주요 공정 라인

현재까지 알려진 정보에 따르면, 25 팹은 다음과 같은 공정별로 운영될 전망이다.

1. P1~P3 공장: 1.4nm 공정

2. P4~P6 공장: 1nm 공정

하지만, 일부 소식통에 따르면 TSMC가 타이중(Taichung) 지역에 1.4nm 공정을 배치하고, 사룬의 P1~P3 공장을 1nm 공정으로 조정할 가능성도 있다.

🚀 GAA 나노시트 기술, 1nm 공정의 핵심!

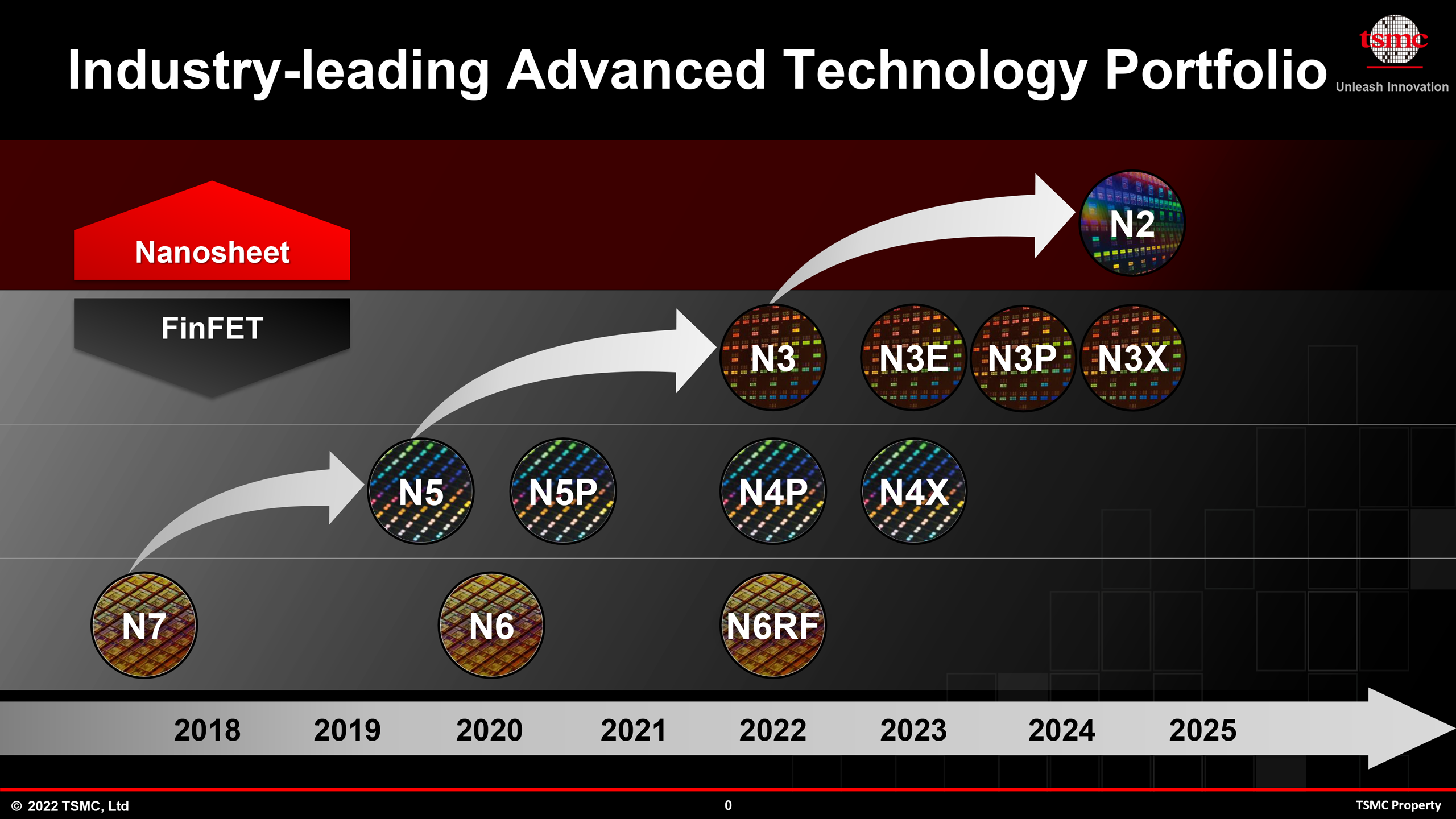

TSMC는 2nm 공정부터 기존 핀펫(FinFET) 구조에서 GAA(Gate-All-Around) 나노시트 트랜지스터 기술로 전환할 예정이다.

📌 GAA 기술이란?

GAA는 기존 핀펫 기술보다 전력 효율과 성능이 향상된 트랜지스터 구조다. 전류가 흐르는 채널을 모든 방향에서 게이트가 감싸는 형태로 설계되어, 전류 제어 능력이 더욱 정밀해지고, 전력 소모도 크게 줄어든다.

📊 GAA 기술의 주요 장점:

1. 성능 15% 향상 → 더 높은 클럭 속도로 동작

2. 전력 효율 30% 개선 → 배터리 수명 증가, 발열 감소

3. 칩 집적도 증가 → 더 작은 면적에 더 많은 트랜지스터 배치 가능

TSMC는 2nm부터 GAA 나노시트(Nanosheet) 기술을 적용하고, 1nm 공정에서도 이를 더욱 발전시킬 계획이다.

📈 1nm 공정 수율과 성능, 어디까지 왔나?

초미세 공정에서는 수율(Yield, 생산된 칩 중 정상 작동하는 칩의 비율)이 가장 중요한 요소다. TSMC는 2nm 공정에서 이미 SRAM 수율 90%를 달성했으며, 1nm 공정에서도 높은 수율 확보를 목표로 하고 있다.

🔹 1nm 예상 수율 & 성능 개선 효과

TSMC가 공개한 예상 수율 및 성능 개선 효과는 다음과 같다.

• ✅ 2nm 대비 성능 15~20% 향상

• ✅ 전력 소비 25~30% 절감

• ✅ 칩 밀도 증가로 동일 면적에서 더 많은 트랜지스터 집적 가능

• ✅ SRAM(Static RAM) 수율 90% 이상 유지 목표

특히 GAA 기술 적용으로 인해 수율이 더욱 안정적으로 확보될 가능성이 높다. 삼성전자가 3nm 공정에서 GAA를 적용하면서 초기 수율 문제가 발생했던 것과 달리, TSMC는 2nm에서 충분한 테스트를 거친 후 1nm에 도입할 예정이기 때문에 초기 수율 이슈를 최소화할 것으로 보인다.

🧐 미국과의 관세 이슈, 1nm 공정에 영향 줄까?

최근 미국 트럼프 전 대통령이 대만산 반도체에 수입 관세 부과 가능성을 언급하면서, 반도체 업계에 긴장감이 감돌고 있다.

💡 미국 관세 부과 시 예상 영향:

• TSMC 고객사(애플, 엔비디아, AMD 등)의 비용 부담 증가

• 반도체 가격 상승 → 소비자 부담 증가

• TSMC의 미국 내 생산 비중 확대 가능성

현재 TSMC는 애리조나에도 반도체 공장을 운영 중이지만, 여전히 대만이 기술력과 생산량 면에서 우위를 점하고 있다. 따라서 관세가 현실화되면, 미국 내 기업들의 반발이 커질 가능성이 높다.

💡 마무리: TSMC, GAA 기반 1nm 공정으로 초미세 공정 선도할까?

TSMC는 타이난 사룬 지역에서 1nm 공장을 건설하며, GAA 기술을 적용한 초미세 공정 시대를 열고 있다.

✔ 2025년 2nm 양산, 2027년 1nm 양산 목표

✔ GAA 나노시트 기술로 성능 & 전력 효율 개선

✔ SRAM 수율 90% 유지 목표, 안정적 생산 가능성 높음

✔ AI 반도체, HPC 시장 겨냥한 초미세 공정 확대

하지만 삼성전자, 인텔과의 경쟁, 그리고 미국 관세 이슈가 변수로 작용할 전망이다. 과연 TSMC가 1nm 공정까지 선점하며 반도체 업계를 주도할 수 있을지, 앞으로의 행보가 주목된다.

'해외토픽' 카테고리의 다른 글

| TSMC 전기요금 10% 인상 추진…대만 전체 전력 소비의 8.96% 차지 (0) | 2025.02.12 |

|---|---|

| 트럼프, 철강·알루미늄 관세 부활… 한국·캐나다 등 동맹국도 영향 (0) | 2025.02.11 |

| 트럼프의 관세 정책, 각국의 반응과 경제적 여파 (0) | 2025.02.03 |

| 트럼프 관세 폭탄, 금값을 사상 최고로 끌어올리다 (0) | 2025.02.03 |

| 미국-멕시코-캐나다, 중국, 그리고 한국: 새로운 관세 전쟁의 서막 (1) | 2025.02.01 |

댓글